3.1. Visión abstracta del hardware

Para conducir un automóvil, se debe familiarizar con algunos elementos clave como los pedales de acelerador y freno, el volante y algunos instrumentos del tablero. De manera colectiva, estos dispositivos le permiten controlar el automóvil y sus diversas partes, así como observar el estado de ciertos subsistemas cruciales. La interfaz correspondiente para el hardware de computadora es su arquitectura de conjunto de instrucciones. Es necesario aprender esta interfaz para ser capaz de indicar a la computadora a realizar tareas computacionales de interés

Después de familiarizarse con el conjunto de instrucciones de una máquina, podrá aprender otros con poco esfuerzo; el proceso es más parecido a mejorar el vocabulario o estudiar un nuevo dialecto del español que aprender todo un nuevo idioma, esto es debido a que a lo largo del tiempo se han desarrollado muchas características de conjunto de instrucciones comunes.

El conjunto de instrucciones MIPS es bastante similar a lo que uno encuentra en muchos procesadores modernos. MIPS es un conjunto de instrucciones load/store (carga/almacenamiento), ello significa que los elementos de datos se deben copiar o cargar (load) en registros antes de procesarlos; los resultados de operación también van hacia registros y se deben copiar explícitamente de vuelta a la memoria a través de operaciones store (almacenamiento) separadas. Por ende, para comprender y ser capaz de usar MIPS, es necesario saber acerca de esquemas de almacenamiento de datos en memoria, funciones de las instrucciones de carga y almacenamiento, tipos de operaciones permitidas en los elementos de datos que se conservan en los registros y algunos otros aspectos sueltos que permiten la programación eficiente.

Para conducir un automóvil no se necesita saber dónde se ubica el motor o cómo acciona las ruedas; sin embargo, la mayoría de los instructores comienzan a enseñar la conducción al mostrar a sus estudiantes un diagrama de un automóvil con sus diversas partes. De forma análoga, la figura 3.1.1 busca el mismo objetivo, posteriormente analizaremos el hardware con mucho más detalle.

Figura 3.1.1 Subsistemas de memoria y procesamiento en un procesador MIPS

Al momento de programar en lenguaje ensamblador trabajaremos con:

- Registros.

- Localidades (locations) de memoria donde se pueden almacenar datos.

- Instrucciones de máquina que operan sobre y almacenan datos en los registros o memoria.

La figura 3.1.1 muestra la unidad de memoria MIPS, con hasta 230 palabras (232 bytes), una unidad de procesamienteo de datos enteros (EIU, Execution & Integer Unit), una unidad de punto flotante (FPU, Floating Point Unit) y una unidad de desvío y memoria (TMU, Trap & Memory Unit). En lecciones posteriores examinaremos a detalle las unidades EIU, FPU y TMU. La EIU interpreta y ejecuta las instrucciones MIPS más básicas (que empezaremos a estudiar) y tiene 32 registros de propósito general, cada uno con 32 bits de ancho; por lo tanto puede direccionar el contenido de una ubicación de memoria (232 bytes direccionables).

La unidad aritmética/lógica (ALU, Arithmetic Logic Unit) ejecuta las instrucciones addition (suma), subtraction (resta) y logical (lógica). Una unidad aritmética separada se dedica a las instrucciones mutliplicación y división, cuyos resultados se colocan en dos registros especiales, llamados "Hi" y "Lo", desde donde se pueden mover hacia los registros de propósito general.

En la figura 3.1.2 se muestra una visión de los registros MIPS. Todos los registros, excepto el O ($0), que retiene permanentemente la constante O, son de propósito general y se pueden usar para almacenar palabras de datos arbitrarias. Sin embargo, para facilitar el desarrollo y compilación eficiente de programas, son usuales ciertas restricciones en el uso de registros. Una analogía útil para estas restricciones es la forma en que una persona puede decidir poner cambio, llaves, cartera, etc., en bolsillos específicos para hacer más fácil recordar dónde se pueden encontrar los artículos. Las restricciones que se usan en los textos clasicos se muestran en la figura 3.1.2.

3.1.2 Registros y tamaños de datos en MIPS

A un elemento de datos de 32 bits almacenado en un registro o localidad de memoria (con una dirección divisible entre 4) se le conoce como word (palabra). Por el momento, suponga que una palabra retiene una instrucción o un entero con signo, aunque más adelante se verá que también puede retener un entero sin signo, un número en punto flotante o una cadena de caracteres ASCII

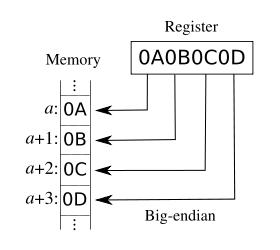

Puesto que las palabras en MIPS se almacenan en una memoria direccionable en bytes, es necesaria una convención para establecer cuál extremo de la palabra aparece en el primer byte (el de dirección de memoria más baja). De las dos posibles convenciones a este respecto, MIPS usa el esquema big-endian (mayor terminación), donde el extremo más significativo aparece primero.

Para ciertos valores que no necesitan todo el rango de una palabra de 32 bits, se pueden usar bytes (ocho bits). Cuando un elemento de dato de tamaño byte se pone en un registro, aparece en el extremo derecho del registro (byte más bajo). Una doubleword (doble palabra) ocupa dos registros o localidades de memoria consecutivos. De nuevo, la convención acerca del orden de las dos palabras es big-endian. Cuando un par de registros retienen una doubleword, el más pequeño de los dos registros siempre tiene un índice par, que se usa para hacer referencia a la localidad doubleword (por ejemplo, se dice "la doubleword está en el registro $16" para dar a entender que su extremo alto está en $16 y el extremo bajo en $17). De modo que sólo los registros con numeración par pueden retener doublewords.

3.1.3 Almacenamiento big endian

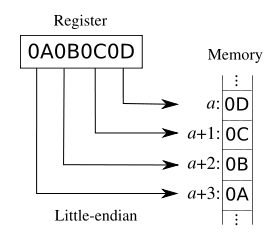

3.1.4 Almacenamiento little endian